新华三李乔:AGI 时代算力基础架构面临的挑战与机遇

新华三李乔:AGI 时代算力基础架构面临的挑战与机遇

目前,人工智能按照进化阶段分为了弱人工智能(ANI)、通用人工智能(AGI)和超人工智能(ASI)三个阶段。自 1956 年麦卡锡、明斯基等科学家首次提出 " 人工智能(Artificial Intelligence,简称 AI)" 这一概念,标志着人工智能学科的诞生;到 2017 年,谷歌 Transformer 模型的发布颠覆了传统的自然语言处理模型,奠定了生成式 AI 的基础;再到 2022 年,OpenAI 正式发布 ChatGPT 并在短短 2 个月内实现了用户数破亿,大量类 ChatGPT 的通用人工智能随之涌现,正式揭开了 AGI 时代的序幕。正如微软 CEO 萨提亚 · 纳德拉所说,"AI 的黄金时代正在到来,并将重新定义我们对工作的全部认识 "。在各个行业中,必将涌现出无数基于类似 GPT-4 这样的通用 AGI 平台的创新应用,重构行业的产品、服务和流程,进而影响我们每一个人的工作、生活和学习。

新华三集团副总裁、互联网事业部总经理李乔

人工智能的三要素包括数据、算法及算力。作为 AI 原料的数据是十分有限的,可利用的公域数据在 2026 年之前就会被大模型全部训练完成。场景化 AI 训练、微调的数据来源将尤其依赖于有价值的私域数据,但私域数据往往是不开放的,隐私计算和联邦学习则将成为打破数据孤岛极为可行的方案,同时合成数据技术的应用也将成为必然。此外,算法复杂度呈指数级增长,模型层数、参数规模快速膨胀的同时也在不断突破。当下,三要素中的算力成为了很多应用落地的最大瓶颈。那么,AI 算力基础架构具体面临哪些挑战与机遇?

PART.1

挑战

在 AGI 时代,数据大模型的参数规模呈现出快速增长的态势。GPT 从 2018 年的 1.17 亿发展到 2020 年的 1750 亿,文心一言 3.0 参数规模达到了 2600 亿,Google 的 Palm 2 参数量也超过 3400 亿。随着参数模型的日益庞大、摩尔定律陷入瓶颈。对计算效率精尽的追逐,使得冯诺依曼模型的先天性不足被成倍放大。计算墙、内存墙、通信墙、能耗墙成为了 AGI 算力基础架构的四大挑战。

首先谈谈 AI 计算的主角 GPU:大模型并行计算量巨大,以 GPU/TPU 代替 CPU 进行大量简单重复计算,虽然计算效率有了明显的提升,但单卡算力和大模型所需总算力之间仍然存在巨大差距。以 GPT-3 为例,每进行一次训练迭代需要消耗 4.5ExaFlops 算力,而主流 GPU 卡单卡算力只能达到 TFlops 级别,百万级别的算力差距便产生了算力墙。分布式训练在一定程度上解决了算力墙问题,但综合考虑 TOC 及不同的 AI 场景,使用专业的芯片和异构计算架构将成为突破算力墙的另一个必要方向。

参数量是衡量模型大小的最关键指标,参数越多对内存的需求越大。以 1750 亿参数的 GPT-3 为例,参数量(FP16 精度)需要 350GB 内存(175B*2Bytes),梯度(FP16 精度)需要 350GB 内存(175B*2Bytes),优化器状态(FP32 精度)需要 2100GB 内存(175B*12Bytes),总计需要 2800GB 内存(350GB+350GB+2100GB),而主流的 GPU 卡仅能够提供 80GB 显存,单个 GPU 无法装下如此庞大的参数量。此外,现有的计算架构以 CPU 为中心,CPU 主内存与 GPU 本地内存无法统一寻址,内存资源相互隔离,GPU 无法高效的使用 CPU 主内存资源,最终导致产生内存墙。

我们在利用大型分布式训练解决算力墙和内存墙问题的同时,又产生了通信墙。不同的并行训练方式下,服务器内及服务器间会分别引入 AllReduce、AlltoAll、梯度数据聚合与分发等通信需求,通信性能强弱将影响整体计算速度的快慢。以千亿级参数规模的大模型训练为例,单次计算迭代内梯度同步需要的通信量就达到了百 GB 量级。此外,AI 大模型训练是一种带宽敏感的计算业务,测试数据表明,采用 200G 网络相对于 100G 网络,会带来 10 倍以上的性能提升。基于以上两方面,一张能够为机间通信提供高吞吐、低时延服务的高性能网络十分重要,服务器的内部网络连接以及集群网络中的通信拓扑同样需要进行专门设计,实现算网的高效协同。

大模型的训练和推理是两头能量怪兽,势必带来极大的功耗。当前业界主流的 8 卡 GPU 服务器最大系统功耗达到 6500W,用于 GPU 服务器之间互联的 128 口 400G 以太网交换机的功耗也接近 3500W。假设 ChatGPT 要满足每天 2.5 亿的咨询量,需要使用 3 万张 GPU 卡,那么,仅仅在推理环节每天消耗的电费超过就超过 50 万(按照每度电 0.8 元计算),因此能耗墙是每个运营者都要面对的现实问题。

算力墙、内存墙、通信墙和能耗墙这四大挑战之间存在一定的关联性,这也决定了我们不能靠简单的堆砌来解决问题,产品架构的系统性设计显得更为重要。紫光股份旗下新华三集团在计算、网络、存储方面都有长期的积累和沉淀,能够系统性地研究和考虑以上的问题,并提出相应解决方案。

PART.2

算力墙应对之道

面对 AGI 时代算力的爆发式增长需求,单一处理器无法同时兼顾性能和灵活度。在此情况下,用最适合的专用硬件去承担最适合的计算任务,并采用异构计算架构去整合这些多元算力,是突破算力墙的有效手段。

在当前的 AI 训练场景,NVIDIA 高端 GPU 是市场上的 " 硬通货 ",其 2023 年发布的 Hopper 架构是 NVIDIA GPU 的集大成者,一经推出便受到市场的青睐。

除了采用 GPU 外,为人工智能业务开发专用的 AI 芯片逐渐成为业界的新趋势。

在 AI 芯片领域,最具代表性的是 Google TPU(Tensor Processing Unit)。发布于 2016 年的第一代 TPU 成为了 AlphaGo 背后的算力担当,当前已经发展到了第四代的 TPU v4。与 GPU 相比,TPU 采用低精度计算,大幅降低了功耗、加快运算速度。

Meta 也发布了 MTIA(Meta Training and Inference Accelerator)自研 AI 芯片,该芯片采用 RISC-V 开源架构,可应用在自然语言处理、计算机视觉、推荐系统等领域。

除了 AI 芯片日益多元化之外,AI 芯片间的高速互联技术也是突破算力墙的关键。

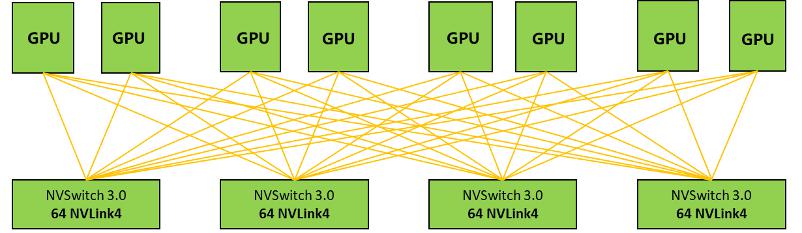

NVDIA 首创了 NVLink + NVSwitch 技术,为多 GPU 系统提供更加快速的互联解决方案。借助 NVIDIA NVLINK 技术,能最大化提升系统吞吐量,很好的解决了 GPU 互联瓶颈。最新的 NVIDIA Hopper 架构采用 NVLINK4.0 技术,总带宽最高可达 900GB/s。

2023 年 5 月 29 日,NVIDIA 推出的 DGX GH200 AI 超级计算机,采用 NVLink 互连技术以及 NVLink Switch System 将 256 个 GH200 超级芯片相连,把所有 GPU 作为一个整体协同运行。

Google 推出的 OCS(Optical Circuit Switch)光电路交换机技术实现 TPU 之间的互联,解决 TPU 的扩展性问题。Google 还自研了一款光路开关芯片 Palomar,通过该芯片可实现光互联拓扑的灵活配置,也就是说,TPU 芯片之间的互联拓扑并非一成不变的,可以根据机器学习的具体模型来改变拓扑,提升计算性能及可靠性。借助 OCS 技术,可以将 4096 个 TPU v4 组成一台超级计算机。

为了满足 AI 加速芯片的互联需求,OCP 组织 2019 年成立了 OAI 开源项目组,通过 OAM 子项目定义业界通用形态的 GPU/AI 模块、对外提供标准通信接口,建立 OAI 相关的技术架构。芯片厂家只要将其 GPU/AI 加速芯片做成 OAM 模块的形态,通过 UBB 来承载多个 OAM 模块,就可以在任何支持 OAM/UBB 模块的服务器上兼容使用。

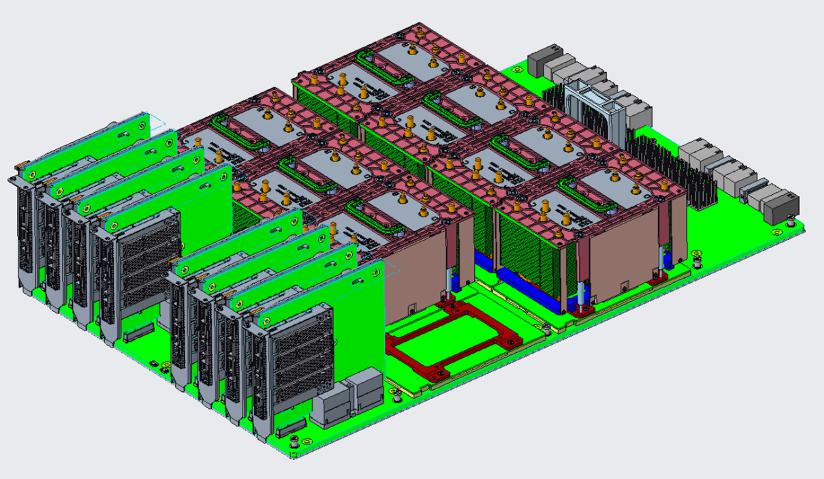

新华三集团作为 OAI 2.0 规范的主要起草单位,在国产化 OAM 方面多有相应的落地实践。那么如何在 AI 算力日益多元化的情况下,如何有效整合这些多元化算力?采用异构计算技术是最佳选择。在异构计算领域,新华三开展了广泛的实践,H3C Uniserver R5500 G6 践行异构计算设计理念,可搭载 Intel 或 AMD CPU,机箱天然兼容 NVIDIA Hopper 架构 GPU 以及 OAI 架构,同时提供对多家厂商 DPU 的支持能力,为不同的应用场景提供了澎湃算力。

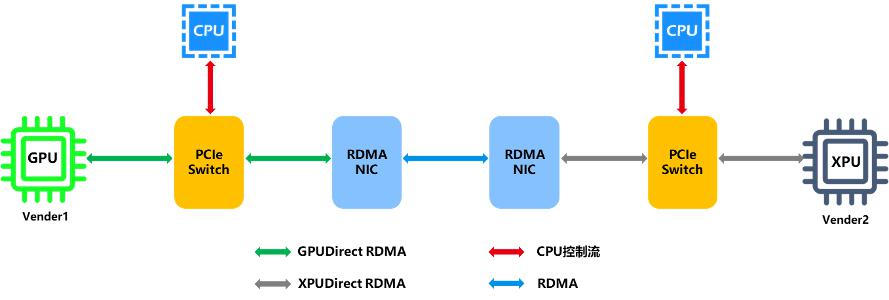

未来,还采用类似 XPU Direct RDMA 的异构芯片通信技术,实现异构计算平台互联。XPU 通信时不再需要 CPU 中转,大幅减少数据拷贝的次数,提升了通信性能,有效整合了多元算力。

PART.3

内存墙应对之道

随着服务器向异构计算架构转型,传统的 PCIe 互联模式已经无法满足高速缓存一致性和内存一致性的需求。GPU 加速卡无法使用 Host 主机自带的内存资源,无法很好的解决 AI 大模型训练场景遇到的内存墙问题。为此,迫切需要在服务器内使用新兴的互联架构,突破内存墙的限制。

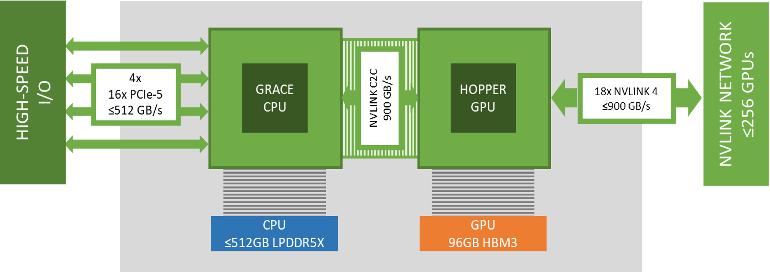

NVIDIA Grace Hopper 架构中,完美的解决了大模型训练的内存墙问题。在该架构中,Grace CPU 和 Hopper GPU 使用带宽高达 900 GB/s NVLink C2C 链路互联,GPU 可以通过 NVLink C2C 透明地访问 CPU 上的 512GB 内存资源。

NVIDIA 通过 Grace Hopper 向业界展现了突破内存墙问题的解决方案。此外,AMD 推出的 Instinct MI300,英特尔推出 Falcon Shores 也采用了类似的解决方案来突破内存墙问题。但这些都属于私有技术。有没有一种开源方案既能解决大容量内存问题和内存一致性问题,又能避免对现有协议体系完全颠覆?Intel 联合其他 8 家科技巨头于 2019 年成立的 CXL(Compute Express Link)联盟就致力于解决该问题。

CXL 是一种开源的互联技术标准,其能够让 CPU 与 GPU、FPGA 或其他加速器之间实现高速互联,并且维持 CPU 内存空间和加速器设备内存之间的一致性,以满足资源共享、内存池化和高效运算调度的需求。CXL 组织已经发布 CXL3.0 版本,其数据传输速率提升至 64 GT/s,并引入了 Fabric 功能和管理、改进的内存池、增强的一致性以及对等通信等重要功能。放眼未来,CXL4.0 基于 PCI-Express 7.0 标准,拥有更高的容量(512GB/S)和更低的延迟,将在性能上实现另一个层级的跃升。

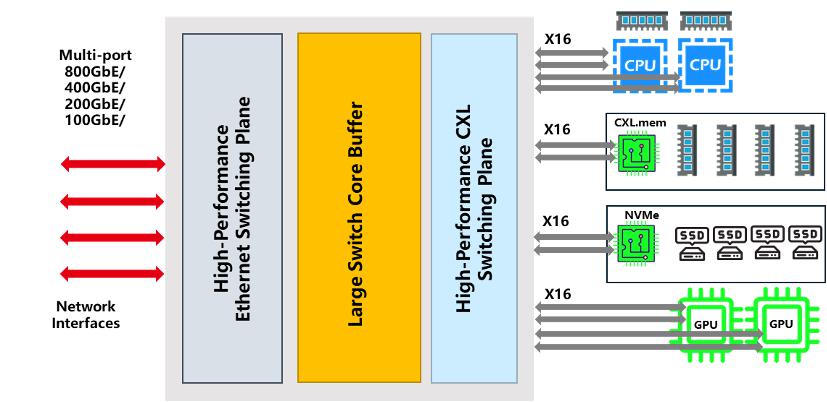

当前,各大上游厂商都在开发或已推出支持 CXL 协议的部件,实现 GPU 显存与主机内存的统一寻址,解决内存墙问题已经近在眼前。畅想未来,随着 CXL Switch 等关键部件的进一步发展,我们可以实现 CPU、GPU、内存等资源的进一步池化,各资源池通过 CXL Switch 互访互通,在集群层面实现全局内存一致性。

新华三集团在 2019 年 4 月正式加入了 CXL 组织,并于 2022 年升级为 Contributor 会员。新华三在 CXL 技术研究上进行了持续的投入,目前正在开展基于 CXL 技术的内存池化、异构互联方面的研究。

PART.4

通信墙应对之道

在集群网络方面,大模型训练优化过的无损网络解决方案可提供高吞吐和低延时的网络服务,确保在大规模训练时集群的性能。

4.1 端网融合的 RoCE 无损网络

RoCE 网络是基于以太网 RDMA 技术实现的,它比 IB 更加开放。RoCE 可以基于现有的以太网基础设施进行部署,网络管理更加简化。但 RoCE 也面临着一些挑战,比如 ECMP 负载不均、哈希冲突、PFC 死锁等。基于 IP 协议的开放性,出现了多种针对 RoCE 的优化方案,其核心思想即将服务器、网卡、交换机作为一个整体,结合创新的拥塞控制算法,实现端网协同。

Google 数据中心使用的 TIMELY 算法,由网卡进行端到端的 RTT 时延测量,根据 RTT 时延数据调整发送速率,实现高性能的 RoCE 网络。TIMELY 算法使用谷歌自研网卡实现,主要应用在 Google 内部。

阿里团队提出的 HPCC 拥塞控制算法,它使用可编程交换机,通过 INT 遥测携带网络拥塞数据,然后由智能网卡动态调整发送速率,获得高带宽和低时延的高性能网络。

EQDS(edge-queued datagram service)是目前被广泛讨论的另一种拥塞控制解决方案。它将网络中的绝大部分排队操作从交换机转移到发送端网卡上,使得交换机可以采用很小的缓存设计。EQDS 由接收端网卡驱动,通过 Credit 机制,来指导数据包发送。另外 EQDS 使用 Packet Spray 实现逐包的负载均衡,以解决负载不均和哈希冲突的问题。如果交换机支持 DCN(Drop Congestion Notification)技术,可以由交换机实现数据包修剪(Packet Trimming),仅将拥塞报文的报文头发送给接收端,接收端接收到报文头后,可以要求发送端快速重传数据包。实验表明,EQDS 在测试中表现出色,能够显著提高数据中心网络的性能。

新华三集团正在研究基于自研服务器、智能网卡和高性能交换机,实现端网融合的 RoCE 无损网络解方案,为 AI 业务提供高性能无损通信网络。

4.2 在网计算

除了通过增加网络带宽、提升链路利用率、优化拥塞控制算法外,在网计算(In-Network Computer)是另一种优化通讯开销的重要手段。在网计算(In Network Computing)可以将 AI 分布式训练的集合通信操作卸载到网络设备上,让网络设备参与计算,减少计算节点之间的消息交互,大幅缩减 AI 分布式训练的时间。

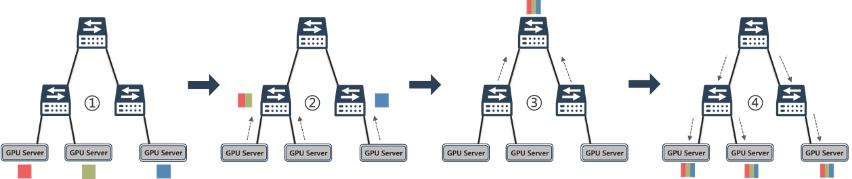

以集合通信中使用频率最高的 AllReduce 规约运算为例,从各节点收集梯度,将训练过程中的汇总规约卸载到集成了计算引擎单元的网络交换机中进行,然后再更新至每一个节点。通过在网计算技术,加速了整个 Allreduce 的过程,可以有效的减少网络拥塞和降低通信延迟。

新华三集团积极投入在网计算技术的研发,借助可编程交换芯片或在传统交换机中引入 FPGA 芯片实现在网计算,提升 AI 训练的整体性能。

4.3 高速以太网及光互联

算力需求的爆发式增长推动了数据中心网络向 800G、1.6T 及更高速率快速演进。光模块作为网络互联的关键部件,随着速率的提升其功耗也一路攀升,在整机系统的占比已经远超 ASIC 加风扇功耗之和。另外,高速光模块在数据中心网络建设中的成本占比也在大幅提升。为了应对由此带来的功耗、成本和时延挑战,业界出现了两种最具潜力的解决方案。

LPO 线性直驱技术去掉了光模块中功耗最高的 DSP 芯片,由交换机 ASIC 芯片来对高速信号进行补偿和均衡,在实现成本下降的同时,大幅降低了光模块的功耗和延迟,非常适合应用在短距大带宽、低功耗低延时的 AI/ML 场景。

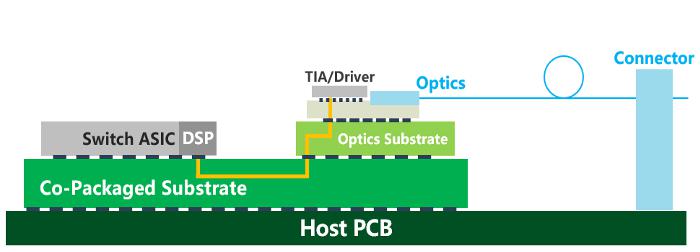

传统可插拔光模块到交换机 ASIC 芯片电信号连接距离较长,途经点较多,累积损耗大。通过 CPO/NPO 等封装技术的引入,显著缩短了交换芯片和光引擎间的距离,同时能够提供更高密度的高速端口,更适合在 1.6T 速率后实现高算力场景下的低能耗、高能效。

在高速互联技术领域,22 年新华三集团发布了采用 NPO 技术的 400G 硅光融合交换机 S9825-32D32DO, MPO 光引擎接口支持 2KM 传输距离,端口功耗降低 40% 以上。

2023 年,新华三集团进一步推出了采用共封装技术的 CPO 交换机,对外提供 64 个 800G 接口或 128 个 400G 接口,并计划今年内支持 LPO 线性驱动光模块的 128 口 400G,64 口 800G 端口的交换机产品。未来,新华三将通过持续的技术创新为 AI 业务提供高性能、低延迟、低能耗的通信网络,破解通信墙的难题。

PART.5

能耗墙应对之道

降低 AI 模型整体能耗的主要方式依然是提高数据中心的散热效率,液冷散热方案因其低能耗、高散热、低噪声、低 TCO 等优势,有着巨大的发展潜力。

其中,浸没式液冷散热是典型的直接接触型液冷,发热元件与冷却液直接接触,散热效率更高,噪音更低。目前,浸没式液冷方案已由初期的单相式液冷进化为相变式液冷,充分利用冷却液的蒸发潜热 , 满足散热极端要求 , 保证 IT 设备满功率运行。

目前,新华三集团在浸没式液冷方案方面完成了全面布局,紧跟互联网业务发展步伐,秉承产学研一体理念,从冷板式液冷到浸没式液冷,从单相式液冷到相变式液冷,从 3M 冷却液到国产冷却液,积极研究跟进推出新华三液冷系统一体化解决方案,包含液冷交换机、液冷服务器、热交换单元、外冷设备等,并且在液冷方案方面持续进行方案迭代和前沿技术探索。

PART.6

展望

本文主要从基础架构角度去讨论如何应对 AGI 时代的挑战。随着数据、算力及算法取得不断的突破,人工智能将会重塑整个经济、社会、产业和人们生活的方方面面。这就需要互联网企业应整合各类资源打造垂直的生态,借助生态伙伴的力量实现科技成果转化,更好地赋能百行百业。作为数字化解决方案领导者,新华三集团具备百行百业的解决方案能力,通过把互联网公司的大模型能力融入到新华三解决方案中,可以开展面向政府、企业、金融、医疗、教育等场景的 N 项业务合作,共同应对快速场景化落地的挑战。

BREAK AWAY

-

- 产业经济显著回暖,信心恢复还需时间

-

2023-06-05 00:37:53

-

- 怎么画房子(怎么画房子?)

-

2023-06-05 00:35:37

-

- 面首是什么意思(为什么古代要把男宠称为面首)

-

2023-06-05 00:33:21

-

- 胆矾是什么物质(“胆矾”的功效及其应用)

-

2023-06-05 00:31:05

-

- 首艘国产大型邮轮将于 6 月 6 日正式出坞

-

2023-06-04 23:57:01

-

- 华为余承东:要用完美主义精神做产品

-

2023-06-04 23:56:25

-

- 五岳之首山东泰山介绍(泰山的主要旅游景点介绍)

-

2023-06-04 06:35:41

-

- 北海旅游攻略必去景点推荐(北海旅游必去十大景点)

-

2023-06-04 06:33:25

-

- 悬赏公告:最高奖励超一千万

-

2023-06-04 06:31:09

-

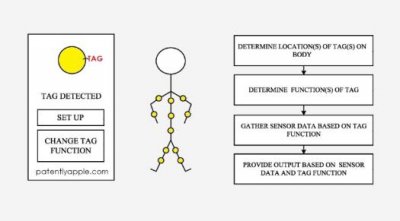

- 苹果 AirTag 新专利曝光:可搭配 HMD 实现全身运动追踪

-

2023-06-04 06:28:54

-

- 巴中美食

-

2023-06-04 06:26:38

-

- “全部退运出境”

-

2023-06-04 06:24:22

-

- 甘孜阿坝州旅游景点有哪些好玩的地方

-

2023-06-04 06:22:07

-

- 金华美食

-

2023-06-04 06:19:51

-

- 未牵绳大狗纠缠女孩,保洁阿姨用身体保护被抓伤,警方回应

-

2023-06-04 06:17:35

-

- 历时 15 个月 AITO 问界达成 10 万辆量产车下线

-

2023-06-04 06:15:19

-

- 五台山求什么最灵验(五台山算命最准的地方)

-

2023-06-03 11:56:59

-

- 蝙蝠是怎么形成的(免疫系统强大的蝙蝠的祖先是谁)

-

2023-06-03 11:54:43

-

- 钓黄尾怎么调漂最有效(黄尾的钓组和用饵要如何选择)

-

2023-06-03 11:52:27

-

- 珠海有什么好玩的地方景点(推荐珠海这6个绝美好去处)

-

2023-06-03 11:50:11

申通快递收费标准价格表2022(申通快递费用查询)

申通快递收费标准价格表2022(申通快递费用查询) 日本第一男吹神,拓也哥(男人在他口中坚持不过3秒)

日本第一男吹神,拓也哥(男人在他口中坚持不过3秒)